Design and Implementation of 4-bit and 8-bit KSA in 18nm FinFET Technology

Objective

The objective is to compute-a small group of intermediate prefixes, then a large group of-prefixes, and so on, until all of the carry bits have been computed. Parallel-prefix structures have been discovered to appeal to adders due to their logarithmic latency.

Abstract

This paper is implemented in the 18nm FinFET model's technology node. It has a high PDP (Power-Delay Product )because it operates at a faster rate than its competitors. The adder is designed and built for bit lengths of 4 and 8, with random input data simulations used to evaluate its operations. Criteria such as power, performance, area, gate count,. Every block used to construct the adder is inspected, and the results are graphically shown. In order to properly examine the parameters, the acquired data is tabulated. All the designs are implemented in cadence virtuoso.

Index Terms—Ripple Carry Adder (RCA), Carry Look Adder (CLA), Carry Increment Adder (CIA), Parallel Prefix Adder (PPA), Kogge-Stone Adder (KSA), FinFET.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

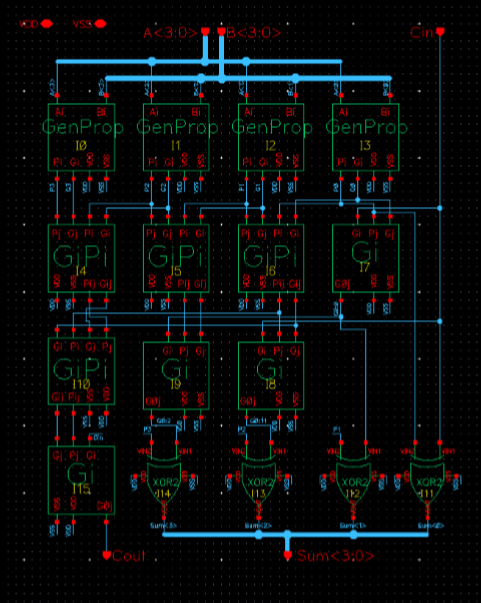

Block Diagram

Specifications

· cadence virtuoso

· Technology files: 45nm

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Introduction to basic gates

· MOS Fundamentals

· NMOS/PMOS/CMOS Technologies

· How to design logic gates circuits using Transistor logic?

· How to design low power, high speed area efficient transistor level logic gates circuits?

· Introduction to Analog Electronics

· Scope of Kogge Stone Adder in today’s world

· Applications in real time

- Cadence virtuoso tool for design and simulation

- Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing