Design and Analysis of Majority Logic Based Approximate Adders and Multipliers

Also Available Domains Arithmetic Core|Xilinx Vivado|Xilinx ISE

Objective

The aim of this project is to implement the high performance adders and multipliers by using Majority logic gates and the multipliers are designed using reduction circuitry like compressors.

Abstract

Approximate computing deals with error tolerance in the computational process as a new paradigm for nano-scale technologies to improve performance and reduce power consumption. Majority logic (ML) is applicable to many emerging nanotechnologies. Its basic building block (3-input majority voting, MV) has been widely used for the design of digital circuits. Designs of approximate adder is evaluated in different complement bits depending on the size of the multiplier, an influence factor is defined and analyzed by a scheme for selecting the complement bits is also presented. The proposed designs will be evaluated using hardware metrics as well as error metrics. The expert compared to other ML-based models found in the technical literature Case studies of systems that are resistant to errors are also provided to illustrate the validity of the proposed models.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

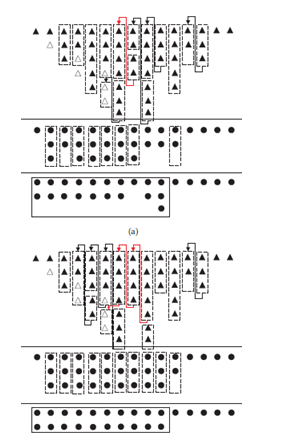

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP,

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Combinational & Sequential circuits

- Knowledge on Arithmetic circuits

- About Approximate Adder multiplier

- Various Majority logic gates

- Knowledge on compressors, adders and multipliers

- Applications of Majority logic based Adder multiplier in real time

- Xilinx ISE for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing