Design and Analysis of Approximate Compressors for Balanced Error Accumulation in MAC Operator

Also Available Domains Arithmetic Core|Xilinx Vivado

Project Code :TVPGTO595

Abstract

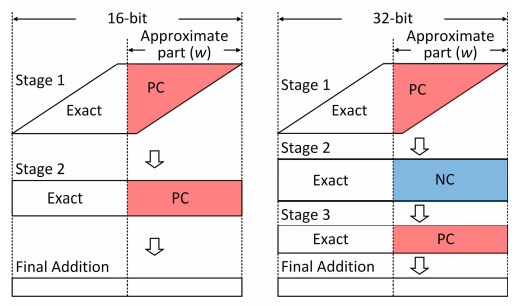

In this project we are going to design

approximate MAC architecture which involves multipliers and adders. In the

conventional multipliers and adders there are many techniques to design where

accurate multiplier is the most power consuming among all arithmetic functional

unit. In this proposed implementation we are going to suggest a novel

approximate structure which leads to reduction of power consumption compared to

the conventional accurate array multiplier. There re conventional approximate

compressors for the designing of approximate multipliers but they limit the

error and the Accuracy obtained is less and UN balanced. Here unbalanced error

signifies the error distance either to b positive or negative which will effect

the accuracy metrics of the compressor there by it will influence the

multiplier accuracy. So to get a balanced error accumulation to obtain a high

accuracy efficiency compared to the conventional approximate multiplier designs

in this suggested or proposed implementation we are going to consider a

positive approximate compressor and a negative approximate compressor

which is obtained by the modification of Boolean expression a of the existing approximate

compressors. For the balanced error accumulation, we first design the

approximate 4-2 compressors generating errors in the opposite direction while

minimizing the computational costs.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7 Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to Arithmetic circuits

- Knowledge on MAC circuits

- Different multipliers and compressors

- Knowledge on compressors and inexact computation

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Demo Video

Related Topics

Paper Publishing

Paper Publishing