CORDIC Architecture For Discrete Cosine Transform

Abstract

In this project, a hardware efficient architecture for Discrete Cosine Transform (DCT) was proposed. Design of less complexity computing hardware architecture for trigonometric and exponential has become challenge for many researchers. CORDIC algorithm has emerged in last decade to provide efficient computing for trigonometric, exponential and logarithmic computations. As the multimedia applications demand high speed and parallel computation of data, the CORDIC algorithm is a suitable computing technique to process such applications. The proposed architecture has been realized using verilog HDL and implemented to capture its design attributes such as speed and design complexity and compared with simple DCT architectures. The effectiveness of the proposed method is synthesized and simulated using Xilinx ISE 14.7\Xilinx Vivado.

Keywords:- FPGA, Discrete Cosine Transform, Hardware Architecture, CORDIC Processor, General Purpose Processor, Digital Signal Processor

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

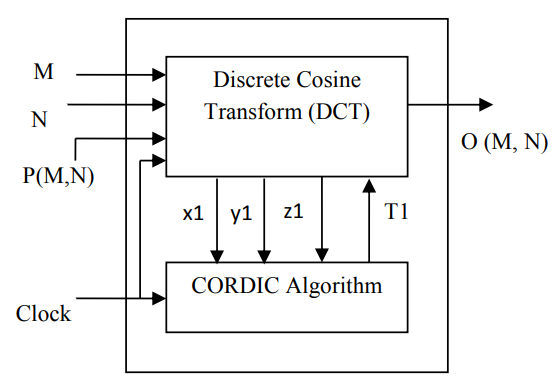

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7\Xilinx Vivado

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to Arithmetic circuits

- Knowledge on CORDIC algorithm

- Different DCT applications

- Knowledge on complex multiplication

- Applications in real time

- Xilinx ISE 14.7/Xilinx Vivado for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing