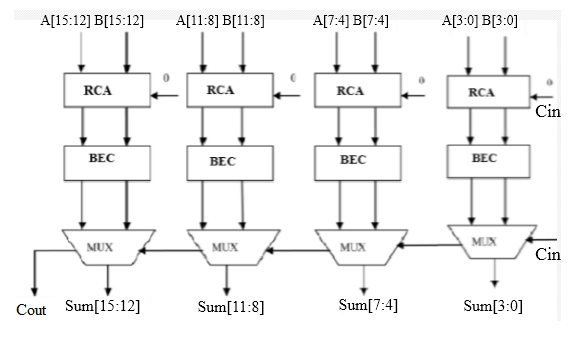

Carry select adder using BEC and RCA

Objective

The main objective of this work is to use Binary to Excess-1 Converter (BEC) instead of RCA in the regular CSLA to achieve high speed and low power consumption.

Abstract

In this we present a design of BEC based carry select adder. In digital adders, the speed of addition is limited by the time required to propagate a carry through the adder. The sum for each bit position in an elementary adder is generated sequentially only after the previous bit position has been summed and a carry propagated into the next position. The Carry select adder (CSLA) is used in many computational systems to lessen the problem of carry propagation delay by independently generating multiple carries and then select a carry to generate the sum. In the proposed method we are implementing a carry select adder by using both BEC and RCA adder. However, the CSLA is not area efficient because it uses multiple pairs of Ripple Carry Adders (RCA) to generate partial sum and carry by considering carry input, then the final sum and carry are selected by the multiplexers (mux). The basic idea of this work is to use Binary to Excess-1 Converter (BEC) instead of RCA in the regular CSLA to achieve high speed and low power consumption .The synthesis and simulation are verified by using Xilinx ISE 14.7 version tool.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP,

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Knowledge on Arithmetic circuits

- Various types of adders implemented in CSA

- Applications of adders in real time

- Study on multiplexers

- Knowledge on carry skip adder, carry select adder and ripple carry adder

- Basic knowledge Binary to excess converter

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing