BIST-Based Low Power Test Vector Generator and Minimizing Bulkiness of VLSI Architecture

Also Available Domains Arithmetic Core|Communications|Xilinx Vivado

Objective

The aim of this project is to present an approach called low power bit complements test vector generation (LP-BCTVG) technique with bipartite (half fixed) and bit insertion (either 0 or 1) techniques. In order to reduce the test power, the LP-BCTVG inserts appropriate intermediate vectors in between consecutive test vectors generated by LFSR circuit.

Abstract

In several pseudorandom built-in self-test (BIST) circuits, the applied test vectors will be generated by a linear feedback shift register (LFSR). This type of test pattern generator (TPG) may generate some repeated test patterns, which unnecessarily increases the test power without contributing much to the fault coverage. Based on the vast designs of TPG engine, the chip area also increases by contributing for the overall power consumption of the IC. This paper presents an approach called low power bit complements test vector generation (LP-BCTVG) technique with bipartite (half fixed) and bit insertion (either 0 or 1) techniques. In order to reduce the test power, the LP-BCTVG inserts appropriate intermediate vectors in between consecutive test vectors generated by LFSR circuit. Hence, the application of final output vectors of LP-BCTVG circuit over circuit under test decreases the test power compared with LFSR-based BIST. By complementing the output bits of LP-BCTVG, we can reduce the bulkiness of TPG engine approximately by half. This further contributes to the reduced IC size. The obtained simulation results prove that this technique can reduce the overall test power consumption along with better fault coverage when compared with LFSR-based BIST and other recent methods

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

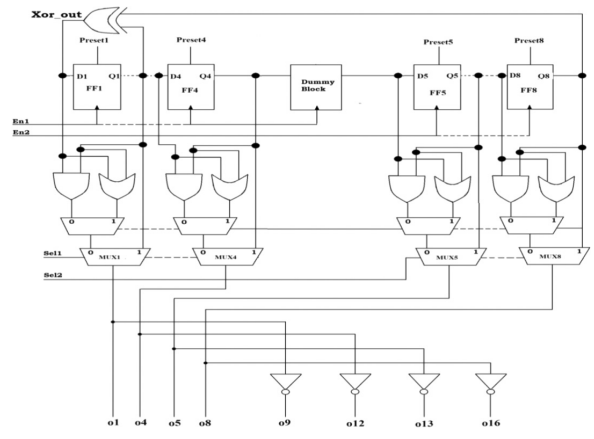

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE 14.7 Tool

· HDL: Verilog

Hardware Requirements:

· Microsoft® Windows XP,

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Concept of BIST

- Importance of TPG

- Drawbacks of existing methodologies

- Introduction to LFSR

- Knowledge on BIST

- Knowledge on various types of LFSR

- Applications of BIST

- Scope of LFSR concept in today’s world

- Applications in real time

· Xilinx ISE 14.7/Xilinx Vivado for design and simulation

· Generation of Netlist

· Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

Thesis Writing Skills

Paper Publishing

Paper Publishing