Area-Efficient LFSR-Based Stochastic Number Generators with Minimum Correlation

Objective

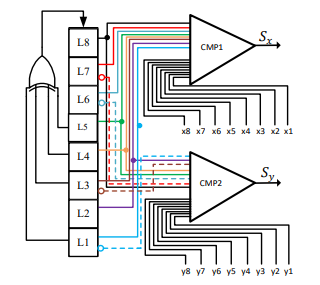

The main objective of this project is to reduce the size of SNGs, we propose a new design approach that shares a combination of the permutations and negations of one LFSR’s output for several SNGs.

Abstract

Abstract

Efficient design of stochastic number generators (SNGs) is critical to the area-efficiency and accuracy of stochastic computing (SC) circuits. Linear feedback shift register (LFSR)- based SNGs are commonly used in SC. To reduce the size of SNGs, we propose a new design approach that shares a combination of the permutations and negations of one LFSR’s output for several SNGs. With no hardware overhead, the approach provides SNGs with minimum average SC correlation (SCC) that result in SC circuits with higher accuracy. Compared to the prior state-of-theart work, our approach produces stochastic bitstreams with 50% less average SCC when a 10-bit LFSR is shared between two SNGs. For an ????-bit LFSR, the proposed design space consists of ????! × ???? ???? designs and when ???? > ???? it is intractable to find the design with minimum SCC by searching the whole space. To address this problem, we propose an optimized search algorithm. For ???? < ????, the extended version of our algorithm can find a set of ???? different designs with minimum SCC values. We apply our approach to SC circuits for digital filters and image processing applications to demonstrate its better computational accuracy and area-efficiency compared to prior work

Keywords: Stochastic number generator, Stochastic computing, Linear feedback shift register, Permutation, Negation

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Processor - Pentium –II

Speed - 1.1 GHz

RAM - 1 GB (min)

Hard Disk - 40 GB

Floppy Drive - 1.44 MB

Key Board - Standard Windows Keyboard

Mouse - Two or Three Button Mouse

Monitor - SVGA

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modelling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Concept of LFSR

- Importance of security

- Drawbacks of existing methodologies

- Applications in real time

· Xilinx ISE 14.7/Xilinx Vivado for design and simulation

· Generation of Netlist

· Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing