Anti-PVT-Variation Low-Power Time-to-Digital Converter Design using 90-nm CMOS Process

Also Available Domains Cadence EDA|Cadence EDA|Tanner EDA

Objective

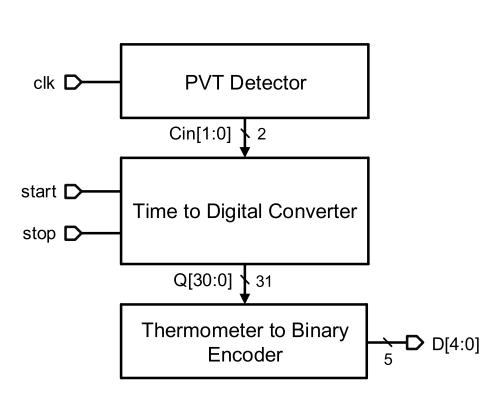

The major contribution of this work is the self-adjustment capability provided by the PVT detector and these codes are used to select the corresponding current-sinking path to reduce delay drift and achieve anti-PVT-variation performance.

Abstract

In this project, a Process, Voltage, Temperature (PVT) variation insensitive TDC featured with a PVT detector is proposed. Recently a lot of research has been carried out on Time to digital converters. TDC has many applications such as time of flight, radar ranging, and particle lifetime measurement.

In TDC, high performance at different PVT corners is needed because it is used in wide range of applications such as ADCs, all-digital PLL, digital converters. The PVT detector takes advantage of another delay line with optimized locking conditions to differentiate PVT corners. The proposed TDC is physically realized using a 90nm CMOS process.

Keywords: Process Voltage and Temperature (PVT), PVT corner detector, Time-to-Digital Converter (TDC).

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Tanner EDA/ Cadence Virtuoso

- Technology files:90nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Introduction to time to digital converters

- Transistors & its applications

- Types of Transistors

- Logic Gates using Transistors

- Pull Up and Pull Down networks

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Analysis of PVT corners and On Chip PVT Variation Models

- Transistor level design for analog to digital converters

- How to design low power, high speed area efficient transistor level circuits?

- Scope of Anti PVT time to digital converters in today’s world

- Applications in real time

- Tanner EDA/Cadence Virtuoso for design and simulation

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing