Analysis of an Efficient Fault Tolerant Linear Feedback Shift Register for Low Power Applications

Also Available Domains Arithmetic Core

Objective

Given the nature of LFSRs in cryptographic systems, the research may aim to maintain or enhance the security properties of the register while improving its reliability and power efficiency. This research paper likely presents a detailed analysis of the proposed fault-tolerant LFSR design, including circuit-level implementations, simulation results, and potential applications in fields such as cryptography, random number generation, or secure communication protocols where reliable and efficient sequence generation is crucial.

Abstract

Abstract:

The method of combining thousands of transistors into a single chip is known as VLSI. The primary purpose of VLSI design is to reduce the area of interconnecting fabrics. The LFSR is one of the most widely used sequence syllogisms since it gives a functional form from its previous state. The conventional LFSR is made up of memory blocks and XORs. The (LFSR) is the core of integrated devices that use patterns of randomly generated bits, such as digitalization clocks, created tests, and pseudo-random number and pseudo-noise sequence generators. For applications that need dependability, fault-tolerant LFSR development is therefore essential. A significant portion of conventional fault-tolerant LFSRs contain SPoFs, meaning that any mistake results in the project's complete failure. A unique fault-tolerant architecture for the single goal failure With a significantly reduced number of SPoFs, the Fault Tolerant-Linear Feedback Shift Register (FT-LFSR) has been designed. In order to differentiate the operating component, this work uses a novel form of Triple Modular Redundancy (TMR) with extra management components. The spatially redundant fault tolerance system known as TMR (Triple Modular Redundancy) was highly effective and popular. TMR's architecture makes it especially difficult to execute a process in parallel, after which the outcome is examined by a mechanism with the biggest group size to produce a single output. Consequently, the likelihood of single number failures is decreased in this recommended method. In addition to its limited SPoFs and other concurrent faults, Xilinx empirical investigations demonstrate that the FT-LFSR is impervious to all individual transient and persistent errors.

Key Words——LSFR, VLSI, Xilinx suit, FT-LFSR

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

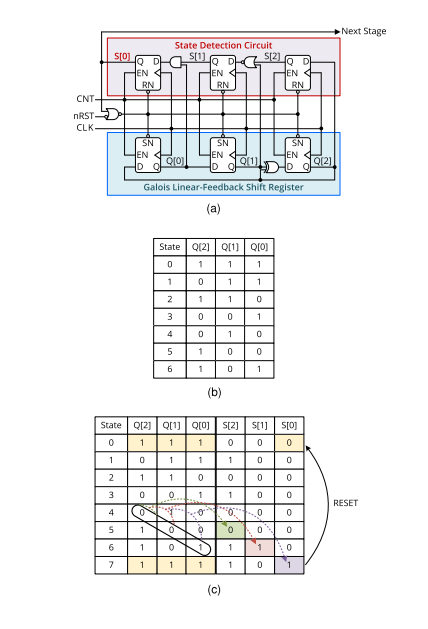

Block Diagram

Learning Outcomes

Learning Outcomes:

• Basics of Digital Electronics

• FPGA design Flow

• Introduction to Verilog Coding

• Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

• Drawbacks of existing methods

• Applications in real time

• • Xilinx Vivado for design and simulation

• • Generation of Netlist

• • Solution providing for real time problems

• • Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

Paper Publishing

Paper Publishing