An Efficient and High-Speed Overlap-Free Karatsuba-Based Finite-Field Multiplier for FGPA Implementation

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

The main aim of this project is to implement the Overlap-Free Karatsuba-Based Finite-Field Multiplier with high speed and area efficiency.

Abstract

Cryptography systems have become inseparable parts of almost every communication device. Among cryptography algorithms, public-key cryptography, and in particular elliptic curve cryptography (ECC), has become the most dominant protocol at this time. In ECC systems, polynomial multiplication is considered to be the most slow and area consuming operation. This article proposes a novel hardware architecture for efficient field-programmable gate array (FPGA) implementation of Finite field multipliers for ECC. Proposed hardware was implemented on different FPGA devices for various operand sizes, and performance parameters were determined. Comparing to state-of-theart works, the proposed method resulted in a lower combinational delay and area–delay product indicating the efficiency of design.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

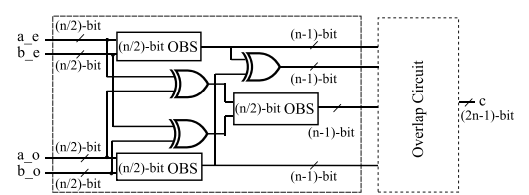

Block Diagram

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Introduction to multiplier design

- Knowledge on multipliers, gates

- About Finite field Multiplication

- About Polynomial Multiplication

- About Karatsuba Algorithm

- Applications in real time

· Xilinx ISE 14.7/Xilinx Vivado for design and simulation

· Generation of Netlist

· Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing