Algorithm Level Error Detection in Low Voltage Systolic Array

Also Available Domains Xilinx Vivado|Xilinx ISE

Objective

The main objective of this paper is to design a systolic array based multiplier to achieve significant improvement in power efficiency.

Abstract

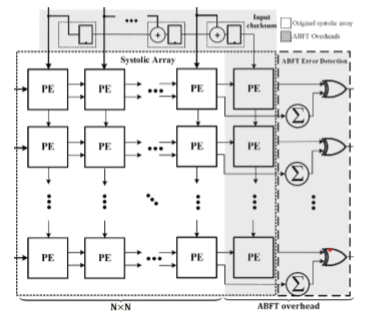

In this brief an approach is proposed to achieve energy savings from reduced voltage operation when implemented in transistor level. In this particular implementation we are going to design a systolic array matrix multiplier where ABFT can be integrated such that it can detect faults. This particular solution detects timing-errors by integrating Algorithm Based Fault Tolerance (ABFT) into a digital architecture when implemented at low level. The approach has been studied with a systolic array matrix multiplier operating at reduced voltages, detecting errors on-the-fly to avoid energy demanding memory round-trips. The design and development of the solution has been done using Verilog HDL and to extract the simulation results of implemented design Xilinx Vivado2018.3/Xilinx ISE14.7suite was considered.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· Xilinx Vivado2018.3/Xilinx ISE14.7 Tool

· HDL: Verilog

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modelling styles in Verilog

o Data Flow modelling

o Structural modelling

o Behavioural modelling

o Mixed level modelling

- Introduction to multiplier design

- About conventional multiplication process

- Knowledge on partial product generation and reduction

- Knowledge on ABFT, error detection

- Applications in real time

- Xilinx Vivado2018.3/Xilinx ISE 14.7 suite for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing