A Unified NVRAM and TRNG in Standard CMOS Technology

Also Available Domains Tanner EDA|Cadence EDA|Core Memories

Objective

The main objective of this project is to present a NVRAM TRNG using a novel mechanism to manage the charges into SFG.

Abstract

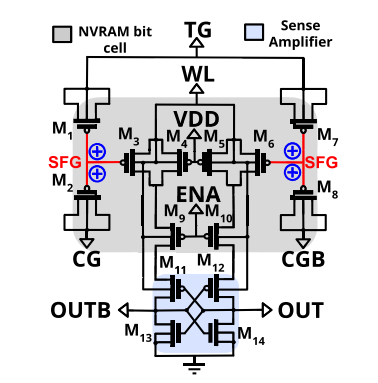

True Random Number Generator (TRNG) provides the different keys for device authentication and cryptography. Typically, the TRNG is implemented in a standalone module into the systems, increasing the complexity and area of the implementation. In addition, the system needs to store the key generated by the TRNG in non-volatile memory for the different applications. However, implementing a Non-Volatile Random Access Memory (NVRAM) requires additional technology features, usually unavailable or expensive. This project presents a unified NVRAM-TRNG in a 45nm standard CMOS technology. The unified implementation does not need additional circuits for the random number generation mode. The differential NVRAM bit cell is implemented using a high voltage transistor to resist the non-volatile memory application. The proposed design has been simulated using the TANNER EDA 13.0 /CADENCE VIRTUOSO.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Learning Outcomes

Learning Outcomes:

- Introduction to NVRAM

- Need of NVSRAM in IOT applications

- Transistors & its applications

o Types of Transistors

o Logic Gates using Transistors

o Pull Up and Pull Down networks

o Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for NVRAM

- How to design low power, high speed area efficient transistor level circuits?

- Drawbacks in CMOS technology

- Scope of NVRAM & Cryptography in today’s world

- Applications in real time

- TANNER EDA 13.0/CADENCE VIRTUOSO tool for design and simulation

- Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing