A Systematic Delay and Power Dominant Carry Save Adder Design

Also Available Domains Cadence EDA|Arithmetic Core|Xilinx Vivado|Xilinx ISE

Project Code :TVMATO795

Objective

The main aim of this paper is to implement carry save adder design based on modified full adder to improve the efficiency of designs as the n bit increases.

Abstract

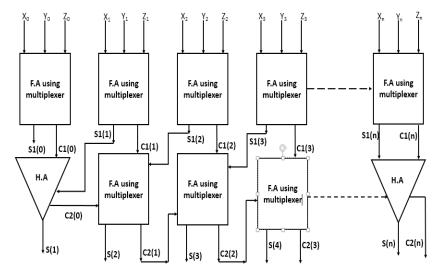

In this project, we propose a new architecture

for carry save adder which is implemented using an adder with multiplexers. In

this the proposed design is developed based on a novel full adder. By making

use of this novel adder design, the overall performance in terms of gate delay

and power consumption of the implementation can be optimized. The

implementation of the CSA in this paper can be designed from 8 to 64 bit

adders. In general RCA is the most common implementation of addition operation.

The major cons of this implementation is it consumes more delay as the bit

width of the implementation increases. The existing full adders are replaced

with the proposed adder and obtain an efficient CSA with improved performance.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx Vivado Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to arithmetic circuits

- Knowledge on full adder and half adder

- Different adders such as RCA, CSLA, etc

- Knowledge on CSA

- Applications in real time

- Xilinx ISE 14.7/Xilinx Vivado/Cadence EDA for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Related Topics

Paper Publishing

Paper Publishing