A High-Performance Multiply-Accumulate Unit by Integrating Additions and Accumulations into Partial Product Reduction Process

Also Available Domains DSP Core|Xilinx Vivado

Objective

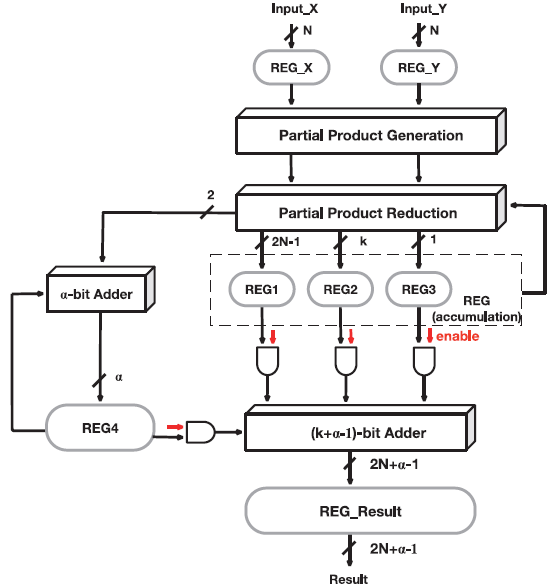

The main objective of this project is to implement a MAC architecture with Low power & reduced delay. The MAC unit was designed with mainly partial product generation and Accumulation units. Hence the delay can be reduced by integrating a part of additions into the partial product reduction (PPR) process

Abstract

In this project, we propose low-power high-speed pipelined Mac architecture. Carry propagation of additions consume more power and large path-delay, to resolve this problem we introduce a proposed method. In this we integrate a part of additions into a partial product reduction process. Until the PPR process of next multiplication, addition and accumulation of MSB bits are not performed.

To correctly contrast with surplus in the PPR process, a small size adder is designed to accumulate the total number of carries. The effectiveness of the proposed method is designed using XilinxISE14.7

Keywords: MAC unit, dadda multiplier, Arithmetic circuits, alpha-bit adder

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- FPGA design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to MAC unit

- About Partial Product Generation

- Partial Product Reduction method for both signed and unsigned numbers

- Knowledge on Adders

- About Registers

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Paper Publishing

Paper Publishing