A Fully Synthesizable All-Digital Phase-Locked Loop with Parametrized and Portable Architecture

Also Available Domains DSP Core|Xilinx Vivado

Project Code :TVPGTO627

Abstract

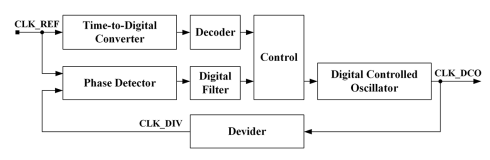

In this project, an all-digital phase-locked

loop (ADPLL) design method based on a new portable architecture has been

introduced. Its motor is a fully synthesizable description of a digital

controlled oscillator (DCO) with variable length ring oscillator (VLRO) as

coarse part and fine-tune unit based on path selector of different pin-to-pin

delays in NAND standard cell. Time to digital converter (TDC) circuit with a

two-level structure has been added to reduce the oscillator frequency's initial

coarse-tune time. TDC allows finding the desired output frequency in two reference

clock cycles. The two-level structure reduces the hardware costs of

implementing this block. The circuit is designed and described in Verilog HDL.

This enables design automation and simplifies the design of digital signal

processing circuits for modern System-on-a-Chip.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

- Xilinx ISE 14.7 Tool

- HDL: Verilog

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

- Data Flow modeling

- Structural modeling

- Behavioral modeling

- Mixed level modeling

- Introduction to PLL

- Knowledge on VCO

- Different types of PLL

- Knowledge on DCO

- Applications in real time

- Xilinx ISE 14.7 for design and simulation

- Generation of Netlist

- Solution providing for real time problems

- Project Development Skills:

- Problem Analysis Skills

- Problem Solving Skills

- Logical Skills

- Designing Skills

- Testing Skills

- Debugging Skills

- Presentation Skills

- Thesis Writing Skills

Related Topics

Paper Publishing

Paper Publishing