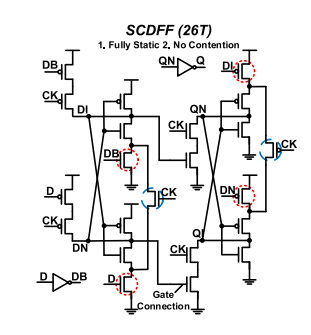

A DIFFERENTIAL FLIP-FLOP WITH STATIC CONTENTION-FREE CHARACTERISTICS IN 28 NM FOR LOW-VOLTAGE, LOW-POWER APPLICATIONS

Project Code :TVPGBE157

Objective

A static contention-free differential flip-flop (SCDFF) is presented in 28-nm CMOS for low-voltage and low-power applications.

Abstract

In the realm of integrated circuit design, the

demand for low-voltage and low-power applications has seen remarkable growth, primarily

driven by portable and battery-operated devices. This paper presents a novel

differential flip-flop design tailored for 28 nm technology nodes. The proposed

flip-flop not only achieves a reduction in power consumption but also exhibits

static contention-free characteristics, ensuring reliable and energy-efficient

operation in low-voltage environments. This research addresses the critical

need for power-efficient and robust flip-flop designs in contemporary

semiconductor technology, promising advancements in the performance of

energy-constrained electronic systems. The experimental results showcase the

viability and advantages of the proposed design, underscoring its potential for

widespread adoption in next-generation low-power integrated circuits.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Specifications:

Software Requirements:

· Tool: Tanner EDA

· Technology: 32nm

Hardware Requirements:

- Microsoft® Windows XP

- Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

- 512 MB RAM

- 100 MB of available disk space

Learning Outcomes

Learning Outcomes:

· Introduction to digital & analog electronics

· Knowledge of MOSFETs

o Operation and characteristics of PMOS & NMOS

o Knowledge on Threshold voltages

· Basics of Sequential Circuits

o Operation of Flip-flops and Latches

o Advantages & Applications

· Knowledge on Tool Learning

· Scope of Flip-Flops in Real time.

Related Projects

Related Topics

Paper Publishing

Paper Publishing