A comparative study of 4-bit Vedic multiplier using CMOS and MGDI Technology

Also Available Domains Cadence EDA

Objective

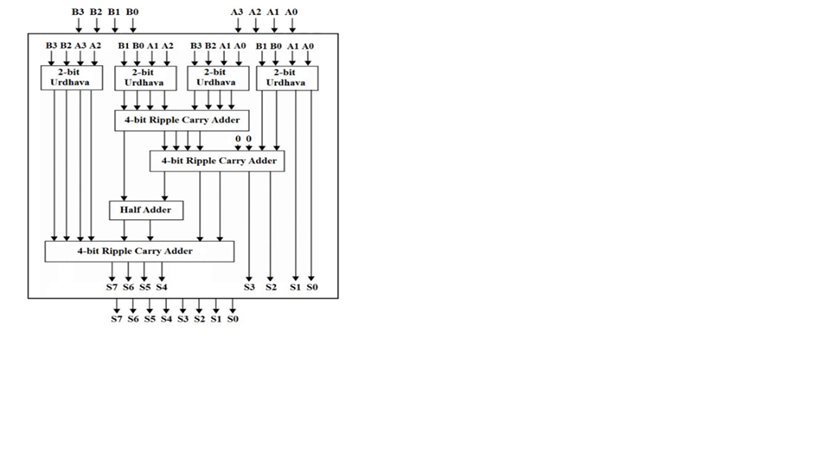

This paper presents the 4-bit vedic multiplier using CMOS and MGDI Techniques. Here, the 4-bit vedic multiplier is designed using 2-bit vedic multipliers, Ripple Carry Adders and a Half Adder.

Abstract

Abstract: In this paper, a 4 bit Vedic multiplier is designed using CMOS technology and MGDI technique. The performance of the system basically works better if the performance of the multiplier is good. In today's digital time, Multiplier is one which consumes power at the same time speed of multiplier is playing very important aspects in this. Multiplier Optimization for power and delay both will play an important role. Adders are also play an important role in the multiplier. Here, we are using Ripple carry adder. In this project, the design is implemented using Cadence Virtuoso tool/Tanner EDA Tool employing gpdk 90nm technology. In this, we perform transient results along with parameters of Area, Delay and maximum power.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Software Requirements:

· Cadence Virtuoso/Tanner Tool

· Technology files: gpdk 90nm

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Logic

- Scope of GDI Technique in today’s world

- Applications in Real time. Introduction to Vedic Multipliers

- Types of ADC

- Limitations & Applications.

- Introduction to GDI.

- Basic GDI & Modified GDI

- Applications

- Introduction to Adders

- Knowledge of designing Adders using various logics

- Ripple Carry Adder

- Full Adder using XOR gates and MUX

- Importance of Transistors

- MOS Fundamentals

- NMOS/PMOS/CMOS Technologies

- How to design circuits using Transistor logic?

- Transistor level design for Vedic multiplier

- How to design Vedic multiplier using GDI Logic.

- Introduction to Analog Electronics

- Importance of GDI

- Cadence Virtuoso tool/Tanner Tool for design and simulation

Paper Publishing

Paper Publishing