8 Bit RISC Processor using Verilog HDL

Also Available Domains DSP Core|Cadence EDA

Project Code :TVMATO411

Abstract

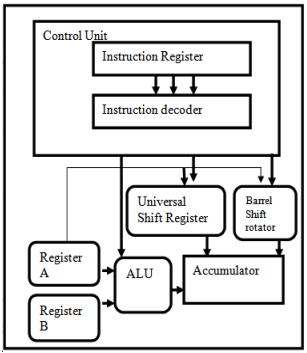

RISC is a design philosophy to reduce the complexity of instruction set that in turn reduces the amount of space,

cycle time, cost and other parameters taken into account during the implementation of the design. The advent of

FPGA has enabled the complex logical systems to be implemented on FPGA. The intent of this paper is to

design and implement 8 bit RISC processor using FPGA Spartan 3E tool. This processor design depends upon

design specification, analysis and simulation. It takes into consideration very simple instruction set. The

momentous components include Control unit, ALU, shift registers and accumulator register

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Xilinx 14.7 for Synthesis, Simulation and

Implementation

Learning Outcomes

- Basics of Digital Electronics

- Verilog HDL

- RTL Designing Skills

- Debugging Skills

Related Topics

Paper Publishing

Paper Publishing