16 Bit Power Efficient Carry Select Adder

Objective

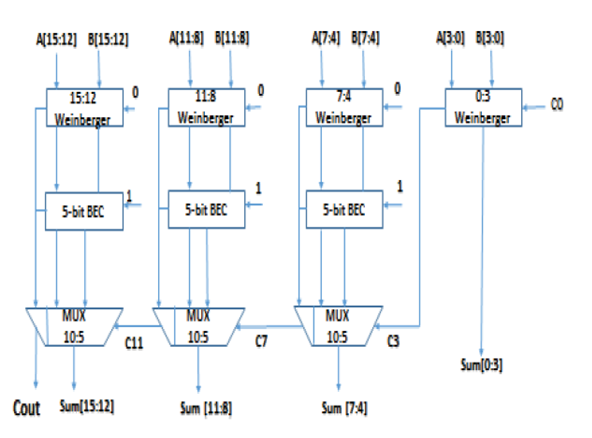

The paper presents a new and modified area and power efficient carry select adder is proposed using Weinberger architecture and it is compared for efficiency with modified Carry Select Adder using Han Carlson, Brent Krung, and Ling adder architectures along with conventional carry select adder.

Abstract

The paper presents a new and modified area and power efficient carry select adder is proposed using Weinberger architecture and it is compared for efficiency with modified Carry Select Adder using Han Carlson, Brent Krung, and Ling adder architectures along with conventional carry select adder. Carry Select Adder proposed here using Weinberger architecture turned out to be the best in terms of area and power. Simulations of all five adder architectures are performed in Xilinx Vivado tool version 14.4 and hardware implementations are performed on zynq 7000 FPGA board which uses 28nm technology.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

Block Diagram

Specifications

Contact Us

- info@takeoffprojects.com

- +91 9030333433, +91 9393939065

Paper Publishing

Paper Publishing