Design of Low-Power Wallace Tree Multiplier Architecture Using Modular Approach

Also Available Domains Xilinx ISE|Cadence EDA

Objective

The main objective of this project is to design a counter based multiplier so that the number of half adders and stages of reduction can be minimized.

Abstract

In this project, we are implementing a power-efficient design of the Wallace tree multiplier using a power efficient 7:3 counter consisting of multiplexer and ex-or gates. Recent development focuses on the design of low-power multiplier for applications like biomedical signal processing requiring the least power consumption and delay-tolerant multiplier. This paper proposes. The maximum power of the multiplier is consumed in the partial product tree reduction, and hence, in the proposed counter-based modular Wallace tree (CBMW) multiplier partial products are reduced using sequential 7:3 counter and the multi-bit addition in a single column reduces the complexity of the multiplier due to improvement in the locality. These proposed changes make design low power and scalable. The hardware utilization is minimum when a single 7:3 counter is used in partial product tree reduction per stage. With the advancement in technology, various designs of multipliers offering low power consumption, high speed and less area have been proposed by many researchers. The main concern of electronic system designers is the energy minimization with the minimum penalty in speed and area for designing portable devices.

NOTE: Without the concern of our team, please don't submit to the college. This Abstract varies based on student requirements.

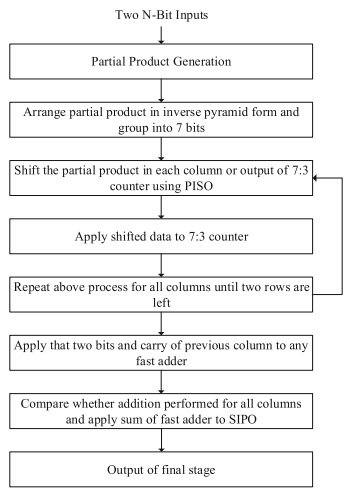

Block Diagram

Specifications

Software Requirements:

· Xilinx ISE/ Vivado2018.3

· HDL: Verilog

Hardware Requirements:

· Microsoft® Windows XP

· Intel® Pentium® 4 processor or Pentium 4 equivalent with SSE support

· 512 MB RAM

· 100 MB of available disk space

Learning Outcomes

- Basics of Digital Electronics

- VLSI design Flow

- Introduction to Verilog Coding

- Different modeling styles in Verilog

o Data Flow modeling

o Structural modeling

o Behavioral modeling

o Mixed level modeling

- Introduction to Arithmetic circuits

- About tree based multipliers

- Knowledge on multiplier architectures

- Different bit width counters or compressors

- Knowledge on multiplier designs using counters or compressors

- About partial product generation and reduction

- Applications in real time

· Cadence for design and simulation

· Generation of Netlist

· Solution providing for real time problems

· Project Development Skills:

o Problem Analysis Skills

o Problem Solving Skills

o Logical Skills

o Designing Skills

o Testing Skills

o Debugging Skills

o Presentation Skills

o Thesis Writing Skills

Paper Publishing

Paper Publishing